AD5340 レジスタ・ストリング型 12bit DAコンバーター

投稿日 2025年05月27日

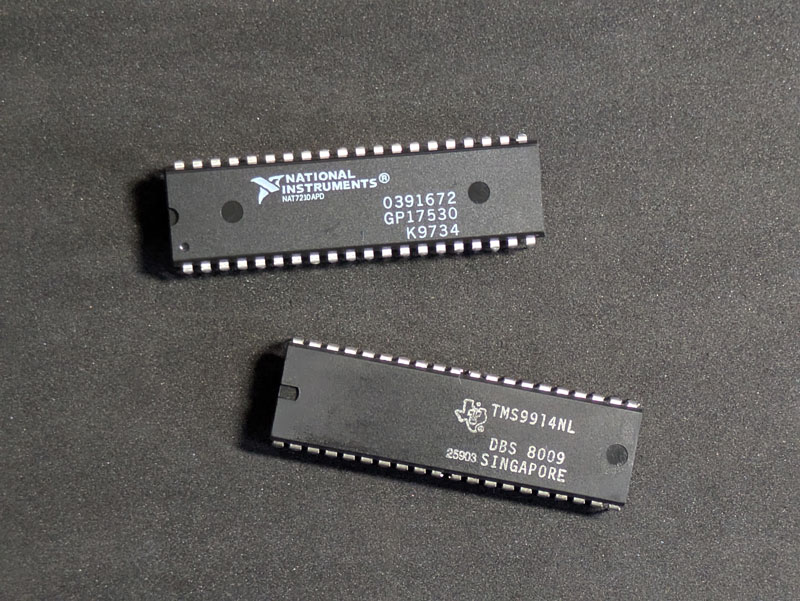

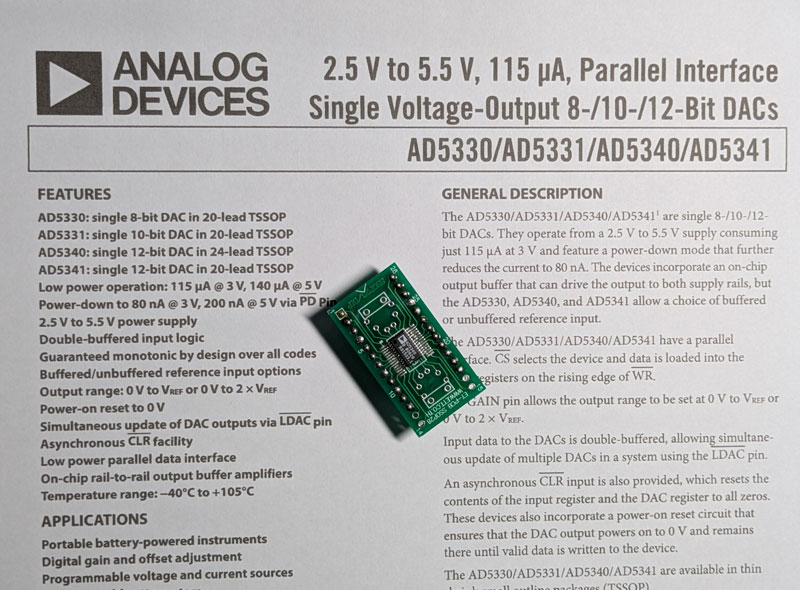

Analog Devices社の12bit パラレル入力 レジスタ・ストリング型DAコンバータ AD5340

24ピンTSSOP

秋月電子のDIP変換基板に搭載

背景はAnalog Devices社 AD53XXのデーターシート

AD53XXシリーズ

先日とり上げたDAC80はR-2R型DAコンバーターでしたが、今回のAD5340はレジスタ・ストリング型のDAコンバーターです。どちらも抵抗分圧した電圧を読み取るという原理は変わりありません。半導体の中にトリミングされた抵抗で構成されますが、R-2R型とレジスタ・ストリング型では必要な抵抗の数が違います。昔は抵抗数の少なくて済むR-2R型が主流でしたが、近年では半導体技術の発達によりレジスタ・ストリング型の製造が可能になりました。その抵抗の数はR-2R型が3N+1個(12ビットの場合37個)で済むのに対して、レジスタ・ストリング型は2のN(レゾリューションのビット数)乗個の抵抗が必要です。12ビットDAコンバーターでは4096個もの正確な値の抵抗が必要となります。

Analog Devices社はAD53XXシリーズとしてAD5330、AD5331、AD5340、AD5341を提供していますが、それぞれ8Bit、10bit、12bitのモデルになっています。AD5340とAD5341はともに12bitですが、AD5340は24ピンのTSSOP、AD5341は20ピンTSSOPとなっており、ピン数の少ないAD5341はデジタルコードを2回にわけてロードするようになっています。今回はこのうちAD5340 12bit レジスタ・ストリング型DAコンバータをすこしいじってみました。

当局のAD5340はどこから入手したのかもう忘れましたが、以前の実験で使用したフォルダのプログラムの更新年月日が2011年になっているので、そのころ入手したようです。TSSOPのチップを秋月電子の28ピンTSOP-DIP変換基板に乗せて、ブレッドボードで実験できるようにしています。二つあるのですが、一方は正常なのですが、もう一方は発熱しながら出力は正常という代物で、なぜこうなったのかは今では不明です。発熱しないほうで実験してみたいと思います。なお、ネットを見るとAD53XXは今でも製造中のようです。

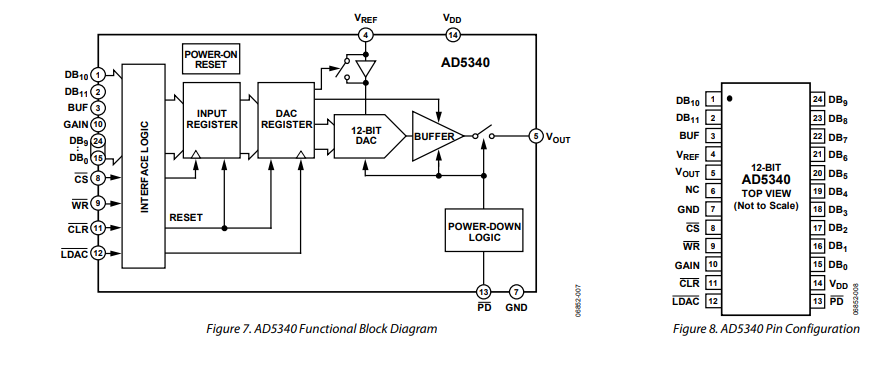

AD5340の回路構成とピン配置

A5340のブロック構成図とピン配置

Analog Devices社 AD53XXのデーターシートから抜粋

AD5340のデジタル・データ(DB0からDB11)は12bitパラレル入力です。リファレンス電圧(Vref)は内蔵されておらず外部から与えます。出力(Vout)は電圧出力です。/CSピン(負論理を/で表します)によりセレクトされている場合のみアクティブとなります。DA変換部の前にINPUT REGISTERとDAC REGISTERがありパイプラインのようにつながっています。/CLRはその二つのレジスタをクリアします。/WRピンの立ち上がりエッジでデジタル・データがINPUT REGISTERにラッチされます。/LDACはINPUT REGISTERのデータをDAC REGISTERに転送します。/LDACを常にLOWに固定しておくと同期モードとなり、INPUT REGISTERの内容は即座にDAC REGISTERに転送され出力に反映されます。/LDACをパルス的にLOWにした場合は、非同期モードとなり、立下りエッジでDAC REGISTERに転送され出力に反映されます。BUFピンはVrefをバッファリングするか否かを決めます。GAINはBUFFER(AMP)のゲインを決めます。LOWの場合ゲインは1(Vref)。HIGHの場合ゲインは2(2Vref)です。BUFとGAINは固定して使うこともできますが、デジタル・データとともに毎回取り込まれ、その変換におけるBUFとGAINを決めます。AD53XXの消費電力(消費電流)はVdd 5Vで0.7mW(140uA)程度です。/PDをLOWにするとパワーダウンモードになり、消費電流が0.2uAに低下します。つまり1uWです。VoutはBUFFER(AMP)から切り離され高インピーダンスとなります。パワーダウンモードになってもレジスタの内容は保持されるため、復帰すれば元の電圧が再現されます。

AD5340の仕様をかいつまんで

AD5340のリゾリューションは12bitです。電源電圧は2.5Vから5.5Vです。相対精度(Relative Accuracy)は 標準 2LSB、最大±16 LSBs。これはIntegran Nonlinearity INLと思われます。INLはオフセット誤差とゲイン誤差を含まない理想直線との差異です。最大16LSBということは、Vref 4.1Vで0.016Vです。微分非直線性(Differential Nonlinearity DNL) は最大 ±1 LSBで単調性(Monotonic)が保証されています。オフセット誤差(Offset Error) は最大±3 % of FSR Vref 4.1Vの場合±0.123Vです。ゲイン誤差(Gain Error) は最大±1 % of FSRでVref 4.1Vの場合±0.041Vです。

基準電圧(Vref)は内臓されておらず、外部から与えますが、内蔵のバッファを通すか否かを選択できます。バッファを通す場合は入力インピーダンスが10MΩ以上となり、外部リファレンスに影響を与えません。バッファを通さない場合、GAIN 1では180KΩ、GAIN 2では90KΩです。

ゲインは1倍、または2倍が選択できます。GAIN 1のとき出力範囲は0.001VからVrefとなります。GAIN 2のとき出力範囲は0.001Vから2Vrefとなります。ただしVdd - 0.001Vを超えることはできません。

電源投入時、出力電圧が0リセットされます。

パワーダウン・モードがあります。通常の消費電流はVdd 5Vのとき250uA以下ですが、パワーダウン・モードのときは1uA以下です。パワーダウン以前のレジスタの内容を保持しており、パワーダウンからの復帰後は出力電圧が再現されます。パワーダウン・モードからの復帰には少し遅延があります。(後述)

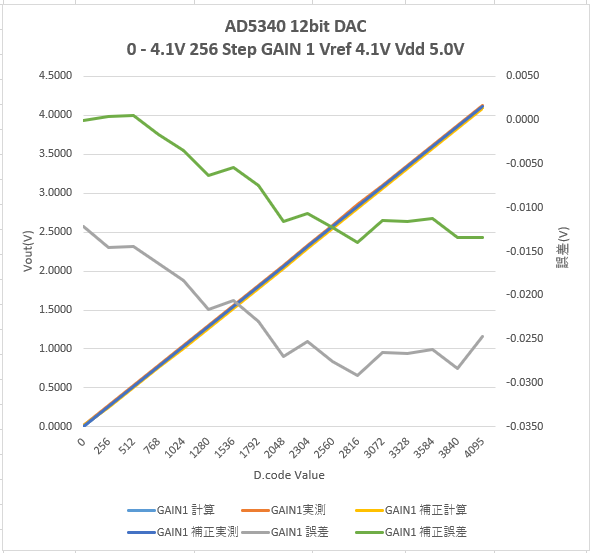

実測してみる

Voutの理想直線とのズレ

Vref 4.1V Vdd 5V GAIN 1

0から4095までのVoutの変化

上側の誤差のグラフ(緑色)はマイコン側で誤差補正したもの

AD5340はオフセット誤差やゲイン誤差を調整する手段はありません。これらは製造時に組み込まれてしまう誤差で、そのまま使わざるを得ません。出力電圧をより理想直線に近づけるために個体の誤差を計測して、与えるデジタル・データに補正を加える必要があります。これはアプリケーション・プログラム側の負担となります。上のグラフは、計算で描いた理想直線、補正せずに実測したデータと、デジタル・コードに若干の補正を加えた出力です。

計測はブレッド・ボードの簡易配線で行っていますので、本来の性能が発揮されているかはわかりません。

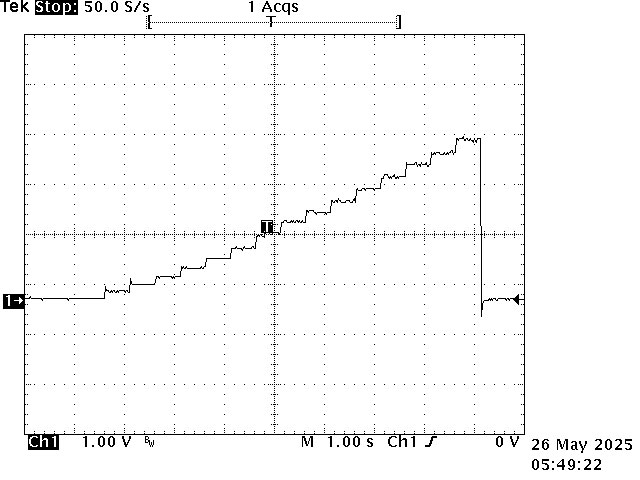

階段波形を作ってみる

階段波形を作ってみました。マイコンはArduino UNOです。UNOはGPIOが14本(0から13)まで使えます。このうち、0から11までをデジタル・コードの入力に使いました。12を/WRに、13を/CLRに使いました。/LDACは配線でLOWに固定しています。つまり同期モードです。後述の出力電圧のセッティング時間の計測では/LDACの立下りからの時間を計測しなければならないので、LSBのDB0(15ピン)をLOWまたはHIGHに配線で固定し、GPIO0を/LDACに割り当てて制御できるようにしました。Vddは外部の低電圧電源で5Vを与えています。基準電圧(Vref)は、TI社のLM4040を使用し4.1Vを得ています。バッファは常にON(BUFF=HIGH)としています。Voutの負荷は2KΩです。以下はデジタル・コードを256ステップ作った階段波形です。

AD5340 256 Step 階段波形

Vref 4.1V Vdd 5.0V

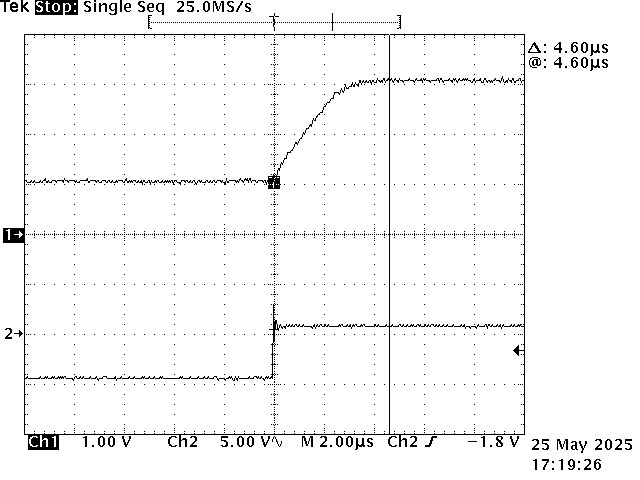

出力電圧のセッティング時間

/WRが立ち上がってからDA出力(Vout)が安定するまでの時間を計測してみました。/LDACは常にLOWですから同期モードです。同期モードではINPUT REGISTERにラッチされたデジタル・データは即座にDAC REGISTERに送られVoutに反映されます。データシートでは、AD5340のSetting Timeは1/4 Scale(0x100)から3/4 Scale(0xC00)への変化時で標準 8us、最大 10usとなっています。実測では4.60usとなりデータシートより早いようです。(AD5340 Vdd 5.0V Vref 4.10V Load 2KΩ Temp 24.5℃ 1/4 Scale = 1.025V 3/4 Sclae = 3.075V)

AD5340 Vout Setting Time (Synchronous)

Ch1 Vout Ch2 /WR

Vdd 5.0V Vref 4.10V Load 2kΩ Temp 24.5℃

1/4 Scale (0x400)から3/4 Sclae(0xc00)への変化時 実測値4.60us

上記はデジタル・コードが1/3 Scaleから3/4 Scaleに変化した場合の速度ですが、0x0000 つまり0Vから0xFFFF 約4.1V(Vref)に変化した場合は7.6us。0x7FFF (Vref - 1LSB) から0xFFFF 4.1V(Vref)への1LSB変化した場合は4.4usでした。このようにデジタル・データによって変換時間が異なります。これのグラフはデーターシートに載っています。

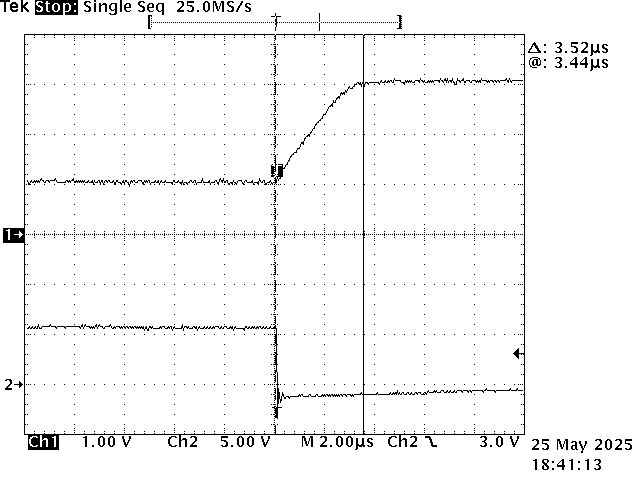

次に、/WRでデジタル・データをINPUT REGISTERにラッチしたあと、/LDACをLOWにしてDAC REGISTERに転送し出力に反映する非同期モードで計測しました。結果、実測 3.52usとなりました。/LDACの立下りエッジから1/4 Scale 0x400 1.025V を保持しているVoutが上昇し始め、所定の電圧(ここでは3/4 Scale 0xC00 3.075V)に安定するまでの時間です。同期モード(/LDACを常にLOWにしておく)よりも1.08us早いようです。この違いはINPUT REGISTERからDAC REGISTERに転送する時間と思われます。(この差はオシロのカーソルの置き方で違ってきますので、正確なものではありません。)

AD5340 Vout Setting Time (非同期モード)

Ch1 Vout Ch2 /LDAC

Vdd 5.0V Vref 4.10V Load 2kΩ Temp 24.5℃

1/4 Scale (0x400)から3/4 Sclae(0xc00)への変化時 実測値3.52us

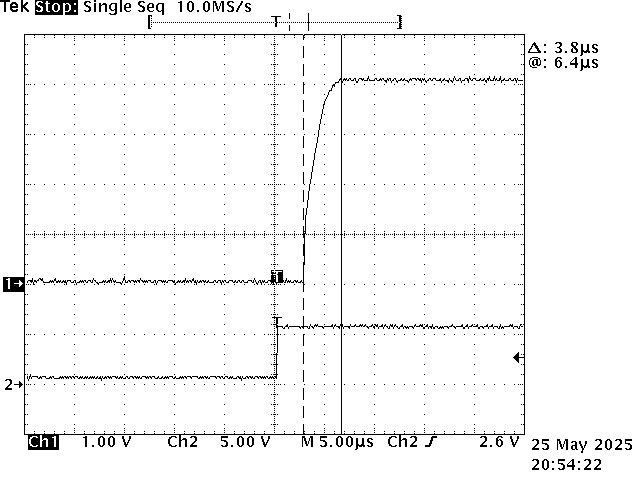

パワーダウン・モードからの復帰

/PDをLOWにするとAD5340はパワーダウン・モードに入り、消費電流が200uA(Vdd 5V)と低消費電力になります。出力はオフとなります。/PDをHIGHにするとすでにDAC REGISTERに入っているデジタル・コードが出力(Vout)に即座に反映されます。このときの遅延時間を計測してみました。あらかじめDACレジスタに0XFFFF (Vref)を入れておき、/PDをLOWからHIGHにしてパワーダウン・モードから復帰させました。実測では、/PDの立ち上がりエッジからVoutが上がり始めるまでに2.6usかかり、そこから3.8usで4.1Vに戻りました。(下記グラフ) DACレジスタに0X7FFF (Vref/2)を入れておいた場合は、/PDの立ち上がりエッジからVoutが上がり始めるまでの2.6usは同じで、そこから2.6usで2.07Vに戻りました。1.2usほど早くなっています。

AD5340 パワーダウン・モードからの復帰時間

Ch1 Vout Ch2 /PD

Voutが立ち上がり始めるまで2.6uS。Voutが戻るまでさらに3.8uS(計6.4us)

Vdd 5.0V Vref 4.10V Load 2kΩ Temp 24.5℃

DAC REGISTERに0XFFFF (Vref )をロードしておき、PWモードから復帰させた

消費電流

AD5430の消費電流はデータシートによるとVdd 5.0Vのとき140uAから250uA、パワーダウン・モードのときは0.2uAとなっています。実測の結果これは出力電圧によって違うようです。GAIN 1で、Voutが0V(DAC REGISTER 0x000000)の場合、約123uA。GAIN 2で148uAでした。VoutがVref 4.1V(DAC REGISTER 0xFFFF)の場合、約218.3uA。GAIN 2で245.4uAでした。また、パワーダウン・モードの場合は、Vout、GAINによらず0.31uAでした。これらにはVerfの外部シャントレギュレータの消費電流は含まれていません。(Vdd 5.0V LOAD 2kΩ)

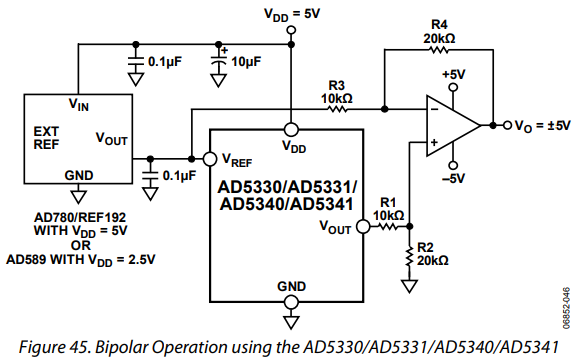

バイポーラにしてみる

AD53XXのデータシートより抜粋

バイポーラ(±5V)で使う場合の回路例

これをVref 1.5Vとし、±3Vのバイポーラ出力とする

GAINは2

AD5340は0からVrefまたは0から2VrefのユニポーラのDAコンバーターですが、データシートにバイポーラで使う場合の回路例が載っています。この回路での出力電圧はVo=((1 + R4 / R3) x (R2 / (R1 + R2 ) x (2 x Vref x D / 2^12 )) - R4 x Vref / R3で計算できます。R1、R3 10KΩ 1%、R2、R4 20KΩ 1%、Vref 約1.5V(乾電池) GAIN2とすると、D = 0のとき-3V。D = 2048のとき0V。D = 4095のとき+2.99Vとなります。GAIN 2によりVoutはVrefの2倍となり、Vrefとの差を2倍の差動増幅器で増幅しています。(Vo = R2/R1(Vref - Vout)) OPアンプはTLC2272CPを使用(Vcc ±5V) 以下は±3Vの256ステップ階段波形です。

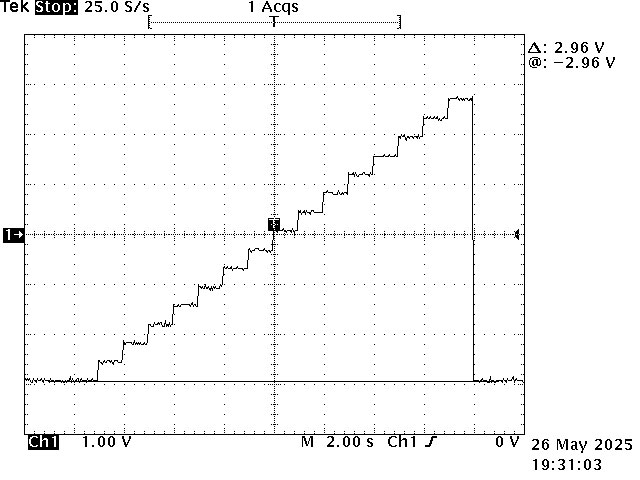

AD5340をバイポーラ ±3Vで使用

Vfer 1.5V Vdd 5.0V GAIN 2 OPアンプ TLC2272CP

256ステップの階段波形

これは、AD5340のデーターシートを個人的に解釈し、動作確認を行ったものです。正確な情報、および最新の情報は別から得てください。

(JF1VRR)